Biography

I am a Post-Doctoral associate in the School of Electrical and Computer Engineering at Cornell University and a member of the Computer Systems Laboratory. My research concerns new algorithms, methodologies, and design automation tools for building correct and dependable computing systems via synergistic applications of specification, architecture, and validation technologies. Specifically, my recent publications focus on post-silicon and pre-silicon validation of System-on-Chips (SoCs), application of machine learning for high-level synthesis and hardware resiliency, and security validation. My research has been recognized with IEEE CEDA Student Research Award (2016) and three best paper nominations (ICCAD'15, DAC'18, ASP-DAC'19).

Prior to joining Cornell, I received my Ph.D. in Computer Engineering from the University of Illinois at Urbana-Champaign (UIUC). I have a B.E in Electronics Engineering from Jadavpur University and an M.S. in Computer Science from IIT Kharagpur.

Research Interests

- Machine Learning for Electronic Design Automation (EDA)

- Reconfigurable Computing, Compiler Optimizations for High-Performance Computing

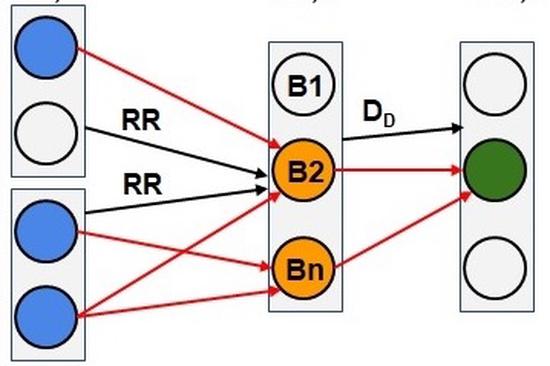

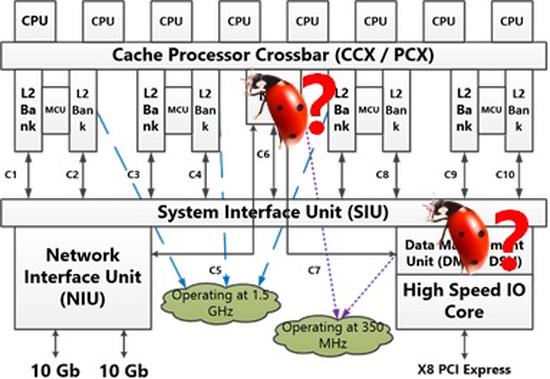

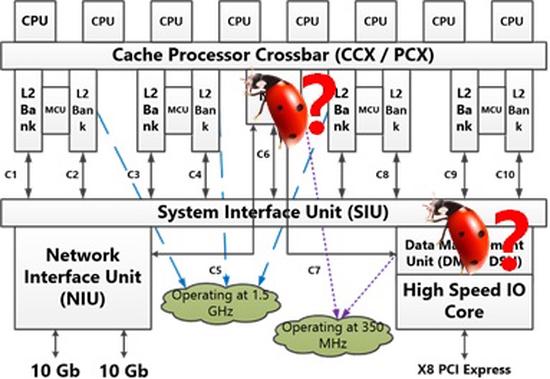

- System-on-Chip (SoC) Verification

- Edge Intelligence (EI) as Service, Trustworthy EI

Education

- Post-Doctoral Associate in Electrical and Computer Engineering (Cornell University)

- Supervisor: Prof. Zhiru Zhang

- Ph.D. in Electrical and Computer Engineering (UIUC 2019)

- Advisor: Prof. Shobha Vasudevan

- Thesis: Scalable Functional Validation of Next Generation SoCs [Talk]

- M.S in Computer Science and Engineering (IIT Kharagpur, 2012)

- Advisors: Prof. Pallab Dasgupta and Prof. Siddhartha Mukhopadhyay

- Thesis: Automated Mixed-Signal Verification using Monitors and Simulation Relations

- B.E in Electronics and Tele-Communication Engineering (Jadavpur University Kolkata, 2008)

- Advisor: Prof. Hiranmay Saha

Professional Services

-

Technical Program Committee (TPC) Member

- Design Automation Conference (DAC) (2021, 2020)

- VLSI Design Conference (VLSID) (2021, 2020)

-

Reviewer

- Journal: IEEE TVLSI (2019, 2018, 2017), IEEE TCAD (2020, 2016), IEEE TC (2019), ACM TODAES (2019)

- Conference: DAC (2019, 2018, 2017, 2016, 2015, 2014), DATE (2021, 2019, 2018, 2017), ICCAD (2018, 2017), FMCAD (2016), IWLS (2020), FPGA (2021), ASPLOS-LATTE Workshop (2021)

Research

Research Themes